Цикл розробки проекту на ПЛІС

Цикл розробки проекту на базі ПЛІС містить у собі декілька етапів:

Створення проекту. При створенні проекту можуть бути використані графічні (.gdf, .bdf) і текстові (.tdf, .vhd, .v) файли. Можливий також імпорт файлів з інших засобів проектування та використання спеціалізованих бібліотек.

У результаті аналізу та компіляції файлів проекту (Analysis & Synthesis) буде отриманий список зв’язків, що дозволяє провести функціональне моделювання проекту, тобто моделювання без урахування затримок сигналів всередині мікросхеми. Даний етап є дуже важливим, оскільки дозволяє проаналізувати працездатність алгоритму.

Далі компанувальник (Fitter) розміщує проект всередині мікросхеми. Після цього з’являється можливість отримати дані про затримки сигналів, максимальні тактові частоти. Ці дані дозволяють провести моделювання з урахуванням затримок сигналу (Timing Analysis), розрахувати спожиту потужність пристрою (PowerPlay Power Analysis) і т.д.

Якщо вимоги по використаній площі кристалу і швидкодії виконані, то генеруються файли для програмування або конфігурування мікросхеми ПЛІС (Assembler (Generate programming file)). Якщо ж вимоги не виконані, то робляться додаткові призначення та установки (Settings & Assignments, Floorplan Location Assignments), а компіляція виконується повторно.

В результаті роботи компілятора на різних етапах генерується декілька файлів, що містять списки зв’язків проекту (Netlist). Розглянемо їх детально, оскільки ці файли використовуються в подальшому для симуляції, часового аналізу та відлагодження проекту.

Pre-synthesis netlist – список зв’язків, який буде отриманий після аналізу проекту, перевірки синтаксису файлів та правильності з’єднань. До цього списку не застосовуються будь-які оптимізації і він містить всі введені користувачем імена.

Post-synthesis netlist – список зв’язків, який отримується після синтезу проекту. Його склад залежить від опцій оптимізації і в ньому можуть бути відсутні деякі сигнали, що були у pre-synthesis netlist.

Post-fitting netlist – список тих зв’язків, що залишись після оптимізації проекту та його розміщення на кристалі ПЛІС. Цей список містить найбільш реальну картину проекту і дозволяє найбільш точно проводити симуляцію та відлагодження.

При розробці проекту на основі ПЛІС можливе спільне використання декількох систем автоматичного проектування. При цьому сполучною ланкою для мікросхем ПЛІС фірми Altera буде пакет Quartus II.

Вигляд пакета Quartus Prime після запуску показаний на рисунку 1.

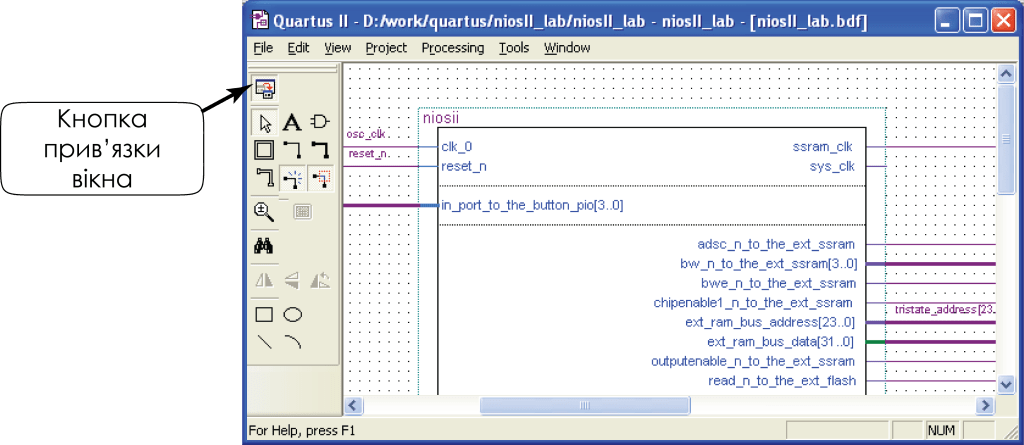

Вікна в пакеті можуть переміщатися незалежно від основного інтерфейсу. Для цього необхідно скористатися кнопкою прив’язки вікна. Для повернення вікна в основний інтерфейс необхідно також скористатися цією кнопкою.

Крім звичного інтерфейсу з кнопковими формами, Quartus Primeтакож підтримує спеціальну мову програмування – TCL (Tool Command Language), на якій можуть бути написані програми (скрипти), які дозволяють прискорити роботу з пакетом та визначення опцій проекту. Для відкриття вікна TCL скриптів необхідно вибрати наступні пункти меню View Þ Utility Þ Windows Þ TCL console (Alt+2).

Створення проекту

При створенні проекту необхідно визначити кілька головних параметрів:

- Каталог, у якому буде збережено проект.

- Назву проекту.

- Назву файлу верхнього рівня ієрархії. Зазвичай це ім’я збігається з назвою проекту.

- Використовувану мікросхему.

- Файли додаткових бібліотек.

- Додаткове програмне забезпечення, яке використовується для симуляції та верифікації проекту.

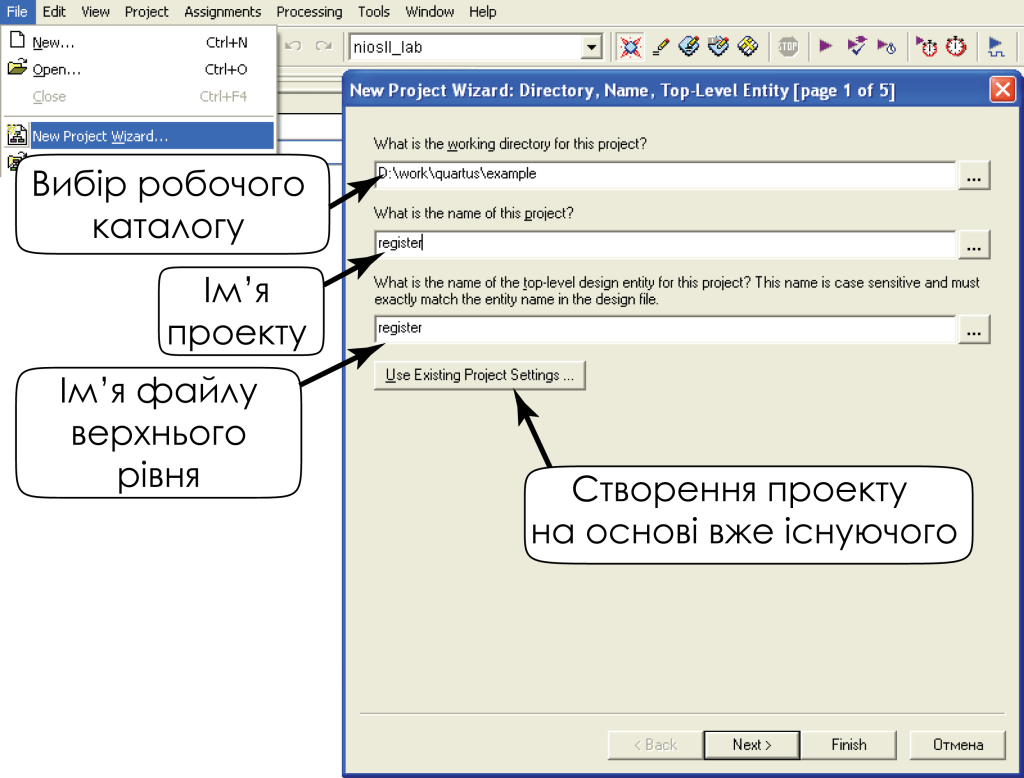

Для створення нового проекту необхідно вибрати пункт меню File Þ New Project Wizard… При цьому буде запущений майстер, за допомогою якого можна буде визначити основні параметри проекту. Розглянемо послідовно призначення діалогів у вікнах майстра проекту. Перехід між вікнами виконується при натисканні на кнопку Next >.

Увага! Пункт меню File Þ New… за замовчуванням та кнопка на панелі інструментів створюють новий файл, а не новий проект!

Перше вікно майстра створення проекту

What is the working directory for this project? – вибір робочого каталогу проекту.

What is the name of this project? – визначення імені проекту. Це може бути будь-яке ім’я, але рекомендується використовувати ім’я файлу верхнього рівня.

What is the name of the top–level design entity for this project? – визначення імені файлу верхнього рівня. При введенні імені слід пам’ятати, що пакет чутливий до зміни регістру.

Use Existing Project Settings… – визначення параметрів проекту на основі існуючого проекту.

Друге вікно майстра створення проекту

У цьому вікні задаються додаткові бібліотеки та файли користувача, які необхідно підключити до проекту. До проекту можуть бути додані файли наступних типів: графічні (.bdf, .gdf), опис схем за допомогою мов опису апаратури (AHDL, VHDL, Verilog), а також файли типу EDIF. Необхідно пам’ятати, що файли, які знаходяться у робочому каталозі проекту, додавати не потрібно. Крім цього можливе додавання бібліотек користувача за допомогою кнопки User Libraries…

Для додавання файлу до проекту необхідно натиснути на кнопку на панелі інструментів, вибрати потрібний файл і натиснути кнопку «Открыть». Обраний файл з’явиться в рядку «File name:». Після цього необхідно натиснути кнопку «Add…» і файл буде доданий до проекту.

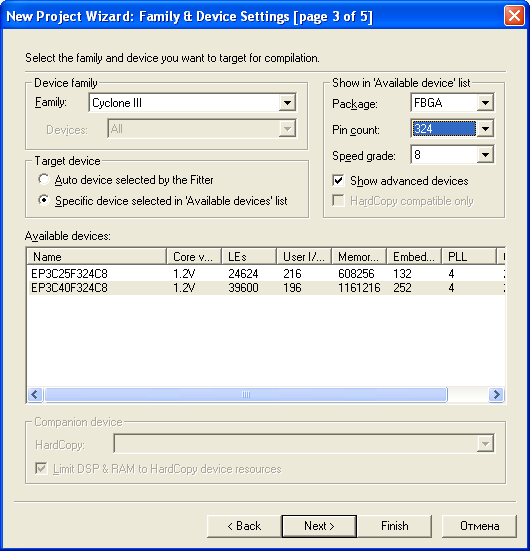

Третє вікно майстра створення проекту

В цьому вікні задаються сімейство мікросхем та параметри мікросхеми з даного сімейства.

Family – задається сімейство мікросхем.

Target device – вибір мікросхеми:

- Auto device selected by the Fitter – автоматичний вибір мікросхеми компанувальником пакету Quartus II.

- Specific device selected in ‘Available devices’ list – вибір конкретної мікросхеми зі списку доступних.

Show in ‘Available devices’ list – вибір параметрів мікросхем, за якими буде формуватися список доступних мікросхем. Користувачу доступні такі фільтри відображення списку мікросхем:

- Package – вибір типу корпусу мікросхеми.

- Pin count – вибір кількості виводів у корпусі.

- Speed grade – визначення градації швидкості.

- Core voltage – відображається напруга живлення ядра мікросхеми.

- Show advanced devices – при включенні цієї опції відображаються тільки мікросхеми з найкращими параметрами.

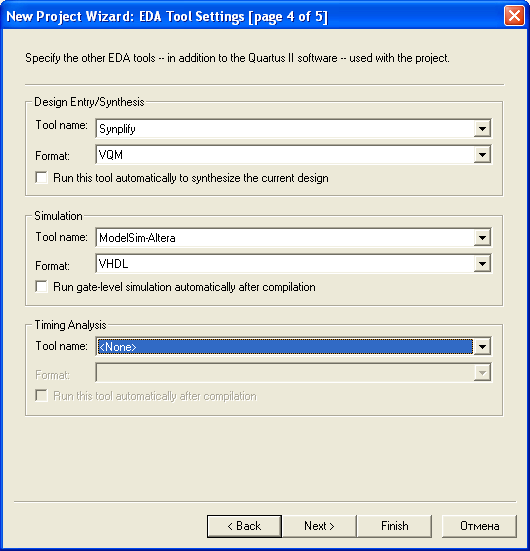

Четверте вікно майстра створення проекту

В цьому вікні робиться вибір додаткових засобів налагодження, верифікації та синтезу проекту. Оскільки при роботі буде використовуватися тільки пакет Quartus II, тому додаткові засоби проектування визначати не будемо.

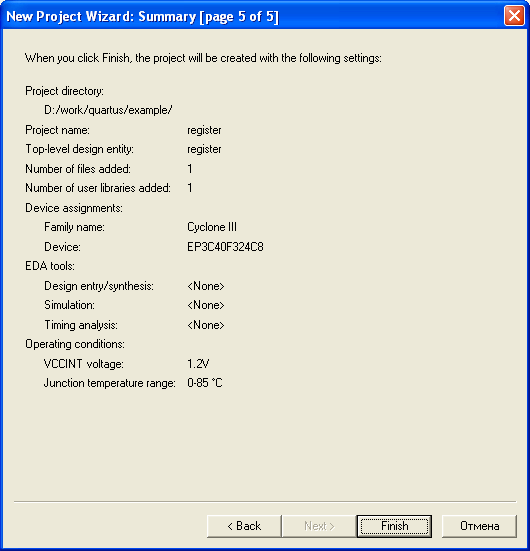

П’яте вікно майстра створення проекту

Це вікно призначене для відображення сумарного результату створення нового проекту. Ніяких дій тут виконувати не потрібно. Натискання на кнопку Finish призводить до створення проекту та закриття майстра.

Відкриття існуючого проекту

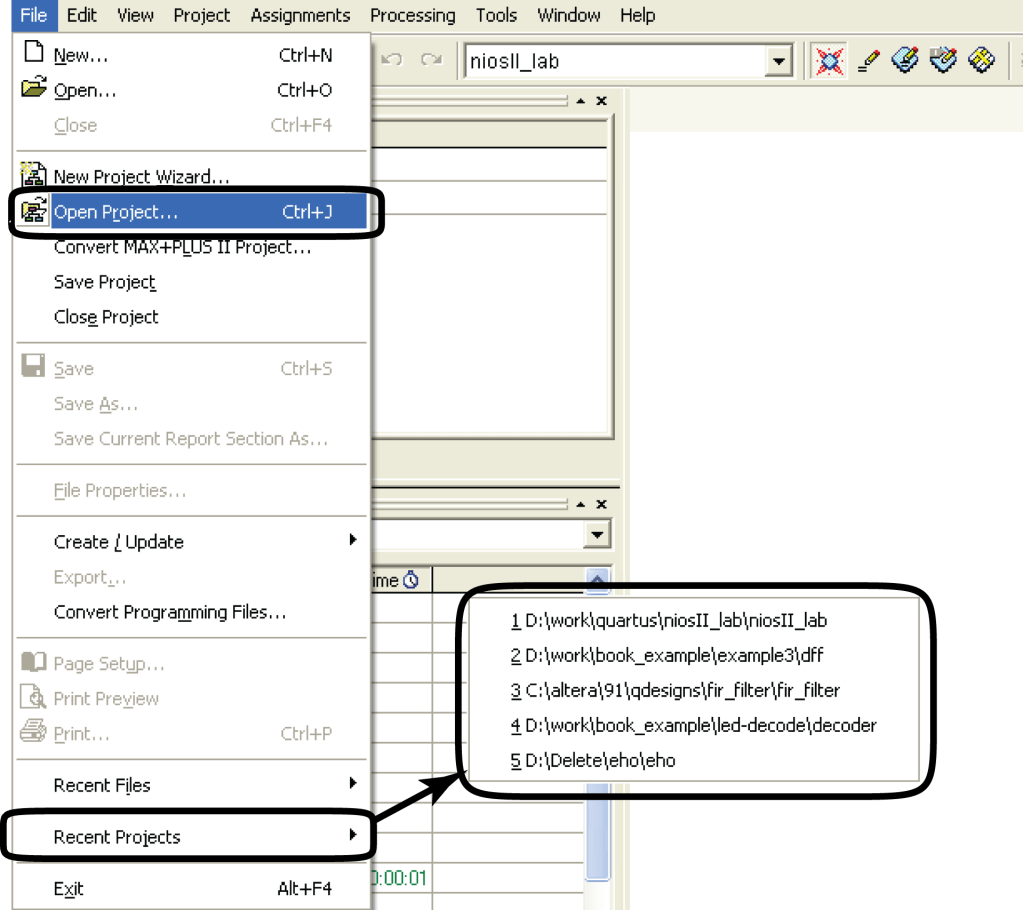

Відкриття нового проекту призводить до закриття попереднього проекту. Тому необхідно зберегти всі зміни в поточному проекті перед відкриттям нового. Відкрити існуючий проект можна декількома способами:

- За допомогою меню File Þ Open Project… У відкритому вікні, що з’явилося, необхідно вибрати файл із розширенням *.qpf.

- Вибрати проект зі списку проектів, які вже відкривалися, за допомогою пункту меню File Þ Recent Projects.

- Використати TCL команду project_open ім’я_проекту.

Необхідно пам’ятати, що відкриття файлу (меню File Þ Open…) та відкриття проекту (меню File Þ Open Project…) не є ідентичними командами.

Відкриття проекту призводить до появи у вікні навігатора проекту його ієрархії.

Навігатор проекту дає можливість переглянути його ієрархію, файли та модулі, що входять у проект. Вікно навігатора проекту складається із трьох закладок:

- Hierarchy – ієрархія проекту (рисунок зліва). Ця закладка використовується для визначення файлу верхнього рівня ієрархії, перегляду використаних ресурсів мікросхеми, пошуку окремої частини проекту в різних редакторах і планувальниках.

- Files – файли (рисунок в центрі). Ця закладка дозволяє відкрити файли, видалити файли із проекту, визначити новий файл верхнього рівня ієрархії, вибрати спеціальні засоби синтезу для файлу.

- Design Units – модулі проекту (рисунок справа). Відображає різні модулі проекту – інтерфейсні та архітектурні тіла різних блоків на мовах опису апаратури.

Створення нового файлу

Для створення нового файлу необхідно скористатися пунктом меню File Þ New… або кнопкою на панелі інструментів. У результаті буде створене вікно вибору типу файлу.

Закладка Device Design Files:

- New Quartus PrimeProject – створення нового проекту.

- AHDL File – файл мовою Altera HDL.

- Block Diagram/Schematic File – файл-схема.

- SOPC Builder System – створення системи на програмувальному кристалі.

- Verilog HDL File – файл мовою Verilog.

- VHDL File – файл мовою VHDL.

Закладка Other Files:

- Memory Initialization File – файл, що містить «прошивку» для пам’яті.

- Vector Waveform File – файл часових діаграм для моделювання роботи проекту.

Створення графічного файлу

Для створення графічного файлу необхідно вибрати пункт Block Diagram/Schematic File у закладці Device Design Files. Це призведе до створення нового файлу.

Всі вікна в Quartus Prime містять закладки, подібні закладкам аркуша в Microsoft Excel. Активна закладка має більш темні кольори. Ліворуч від вікна графічного редактора розташована панель інструментів. Закладка може розташовуватись і окремо від загального вікна пакету Quartus II. Для цього необхідно натиснути кнопку прив’язки вікна. Для повернення вікна назад, до загального вікна пакету необхідно натиснути кнопку прив’язки ще раз.

Саме поле графічного редактора заповнене сіткою, параметри якої можуть бути встановлені за допомогою категорії Block/Symbol Editor меню Tools Þ Options…

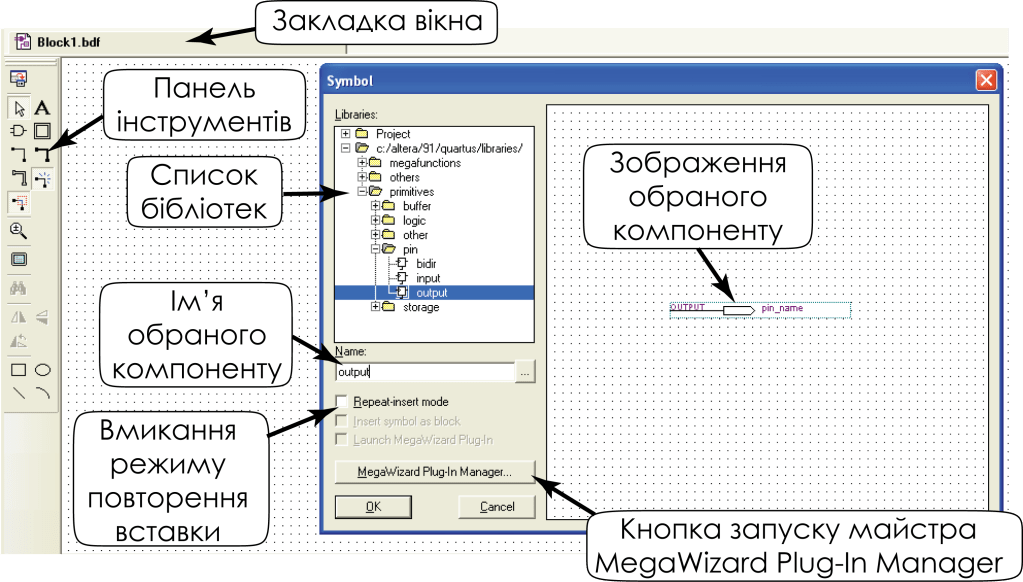

Для вставки символу у файл необхідно натиснути кнопку вставки символу або виконати подвійне клацання по порожньому місцю на робочому листку. При цьому з’явиться вікно вставки символу.

Для вибору символу можна ввести його ім’я в поле Name: або вибрати символ зі списку доступних бібліотек, що відображуються в полі Libraries. У полі Libraries відображаються символи, які містяться в робочому каталозі проекту, символи з інших бібліотек, а також символи зі стандартних бібліотек, які встановлюються разом з пакетом.

За замовчуванням користувачу доступні такі бібліотеки:

- primitives – бібліотека примітивів:

- buffer – буфери SOTF, WIRE, LCELL, GLOBAL і т.д.

- logic – логіка: елементи І, АБО, НІ і т.д.

- other – примітиви землі (GND), живлення (VCC), константи;

- pin – виводи: вхід (INPUT), вихід (OUTPUT), двонаправлений (BIDIR);

- storage – тригери;

- other – інші примітиви.

- maxplus2 – примітиви 74 серії. Не рекомендується для застосування.

- megafunctions – мегафункції, які використовуються майстром MegaWizard. Склад бібліотеки буде описаний нижче.

Як приклад розглянемо побудову схеми, показаної на рисунку.

Для малювання цієї схеми знадобляться наступні примітиви:

NAND2 – елемент 2І–НІ;

INPUT – примітив входу;

OUTPUT – примітив виходу.

Створення схеми

Створіть графічний файл (Block Diagram/Schematics File).

Виконайте подвійне клацання та вставте необхідні примітиви. При роботі в редакторі можливе використання миші в режимі «натиснути і перетягнути».

З’єднання елементів. Для з’єднання елементів схеми немає необхідності переходити в режим малювання провідника. Якщо підвести курсор до виводу елемента, біля курсору з’явиться зображення значка на кнопці малювання провідників. Натискаючи на ліву кнопку миші, з’єднайте елементи так, як показано на рисунку вище.

Для визначення імені провідника необхідно вибрати провідник і натиснути праву кнопку миші. У контекстному меню, що відкрилося, необхідно вибрати пункт «Властивості» (Properties) (рисунок 15). У вікні, що відкрилося, Node Properties у вкладці «Загальні» (General) у поле Name необхідно ввести ім’я провідника. У випадку використання групи провідників необхідно використовувати ті ж правила, що прийняті для контактів.

Перейменування входів та виходу. Для перейменування входів та виходу необхідно виконати подвійне клацання по входу, що призведе до відкриття діалогу, показаного на рисунку 16.

Тут:

- Pin name(s) – ім’я контакту або контактів.

- Default value – значення за замовчуванням, тобто значення, що буде подаватися на контакт у тому випадку, якщо він залишився непідключеним. При цьому необхідно пам’ятати, що таке значення стосується тільки внутрішніх вузлів схеми. Зовнішні виводи повинні управлятися елементами вводу–виводу.

У тому випадку, коли необхідно задати групу контактів, то їхню назву вводять у наступному форматі: ім’я_контакту [старший_розряд .. молодший_розряд].

Наприклад: аddr[7..0], count[16..8].

У записах груп контактів у програмному забезпеченні фірми Altera прийнято записувати старший значущий біт ліворуч, а молодший значущий біт – праворуч. Зворотний порядок призводить до появи попередження (Warning).

Для звернення до окремих контактів із групи варто користуватися наступним форматом: ім’я_контакту [номер_розряду].

Наприклад: аddr[7], addr[5], count[10].

Введіть у поле Pin name(s) значення відповідно до рисунка.

Збереження схеми. При збереженні Quartus Primeзапропонує ім’я файлу, яке співпадатиме з ім’ям проекту. Якщо файл є файлом верхнього рівня ієрархії (Top-Level Entity), то змінювати його не потрібно. В усіх інших випадках бажано, щоб ім’я файлу було унікальним і не повторювало назви компонентів у проекті і самому файлі.

Компіляція проекту

Процес компіляції в пакеті Quartus Primeу своєму типовому вигляді може бути описаний за допомогою алгоритму, показаного на рисунку 1 До цього процесу можуть бути додані додаткові модулі, призначення яких визначається програмним забезпеченням інших виробників.

Запуск компілятора здійснюється або при натисненні кнопки, або вибором пункту меню Processing — Start Compilation. У цьому випадку буде виконана повна компіляція. Однак, можливий запуск окремих складових компілятора. Для цього необхідно вибрати пункт меню Processing — Start.

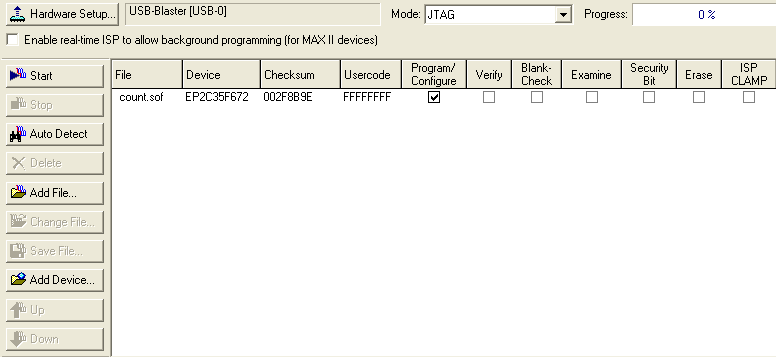

При конфігуруванні ПЛІС необхідно використати конфігураційний файл, для створення якого використовується модуль Assembler. Для його запуску необхідно або виконати повну компіляцію проекту або вибрати пункт меню Processing Þ Start Þ Start Assembler. Файли створені в процесі роботи модуля Assembler, необхідно завантажувати в ПЛІС за допомогою модуля Programmer.

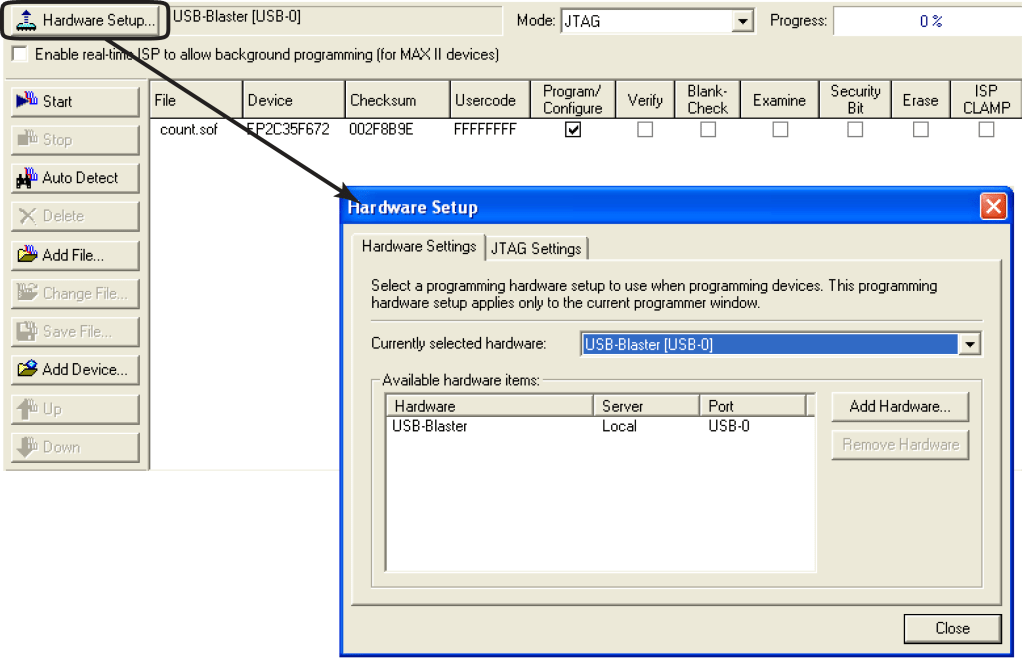

У результаті буде відкрите вікно програматора.

Робоче поле модуля Programmer містить наступні опції програмування:

- Program/configure – програмування або конфігурування мікросхеми.

- Verify, Blank–check, Examine, Erase – перевірка конфігурації в мікросхемі, стирання, контроль стирання конфігурації – для мікросхем сімейств MAX II, MAX 7000, MAX 3000 та конфігураційних ПЗП.

- Security bit – встановлення біта таємності

Даний модуль також дозволяє визначити використовуваний завантажувальний кабель.

При роботі з пакетом Quartus Primeможливе використання наступних завантажувальних кабелів: Byteblaster II, Byteblaster MV, Usb-blaster, Masterblaster cable. Ці кабелі можуть підключатися до різних апаратних портів вводу–виводу персонального комп’ютера: LPT, COM, USB.

При першому ввімкненні модуля Programmer необхідно зробити вибір використовуваного завантажувального кабелю. Для цього необхідно натиснути кнопку Hardware Setup… У вікні, що відкрилося, можна вибрати підключений кабель зі списку Currently selected hardware (поточний обраний апаратний засіб). Для додавання обраного завантажувального кабелю необхідно натиснути кнопку Add Hardware… Подальші операції з конфігурування містять в собі наступні етапи:

- Вибір необхідного конфігураційного файлу (за замовчуванням відкривається файл, необхідний для завантаження в обрану мікросхему. Тому даний пункт найчастіше немає необхідності виконувати).

- Установка опції Program/Configure.

Натискання кнопки Start

Створення опису логічних рівнянь за допомогою мови Verilog.

Основним елементом Verilog HDL є модуль (module). Кожен модуль описує якийсь пристрій або ж його частину. Вихідний код модуля, показаний в лістингу 1.1.

Назва модуля записується після слова «module». Ім’я модуля повинно співпадати з ім’ям файлу. Будь-яке цифровий пристрій містить зовнішні контакти. Аналогом цього в Verilog HDL є входи (inputs) і виходи (outputs). Для нашого пристрою — це «KEY» і «LED».

Листинг 1.1 – Схема з логічними елементами

module lab1

(

input [4:1] x, // KEYs

output LED // LED0

);

wire [3:0] eq;

assign eq[0] = ~( x[1] & x[2] | x[2] | x[3] );

assign eq[1] = ~( x[2] & x[4] | ~x[1] );

assign eq[2] = ( x[1] & ~x[2] & x[3] & ~x[4]);

assign eq[3] = (~x[1] & ~x[2] & x[3] & x[4]);

assign LED = eq[0] | eq[1] | ~(eq[2] | eq[3]);

endmodule

Входи і виходи в пристрої можуть бути як однорозрядні, так і багаторозрядні. Приклад однорозрядного входу:

input rst_n,

Для багаторозрядного входу або виходу запис буде виглядати так:

input [1: 0] KEY, // KEYs

output [3: 0] LED // LEDs

У квадратних дужках вказують кількість біт – два для входу KEY і чотири для виходу LED. Це означає, що два сигналу від кнопок будуть підключені до входів модуля, а чотири вихідні сигнали будуть підключені до світлодіодів.

Всередині модуля вхідний сигнал управляє провідником (wire). У нашому прикладі це чотири сигнали: «eq» з номерами від 3 до 0.

Наведемо схему з використанням логічних рівнянь. Наприклад, опис логічного І виглядає так:

assign LED [0] = a & b;

Це означає, що вихід «led [0]» буде управлятися логічним І від «a» і «b».

Оператор «assign» задає безперервне присвоювання значення сигналу. «Безперервне» означає, що будь-яка зміна одного з операндів в правій частині виразу відразу викликає зміна значення вихідного сигналу. Цей вид присвоювання завжди синтезується в комбінаційну схему.

Більш складне логічне рівняння буде виглядати так:

assign eq[2] = ( x[1] & ~x[2] & x[3] & ~x[4]);

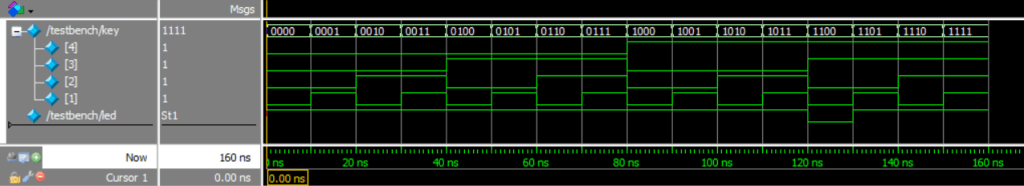

Створіть тестбенч для вашої лабораторної роботи. Тестбенч (Testbench) – це тестове оточення для перевірки правильності функціонування вашого проекту. Тестбенч генерує набір сигналів для нашого пристрою, а потім отримує сигнали від пристрою. Розглянемо код тестбенчу (Лістинг 1.2) для моделювання схеми, що описується таблицею дійсності 1.1.

Лістинг 1.2 Модуль ‘testbench.v’

`timescale 1ns / 1ps

module testbench;

// input and output test signals

reg [4:1] key;

wire led;

// creating the instance of the module we want to test

// lab1 — module name

// dut — instance name (‘dut’ means ‘device under test’)

Lab1 dut ( key, led );

// do at the beginning of the simulation

initial

begin

key = 4’b0000; // set test signals value

#10; // pause

key = 4’b0001; // set test signals value

#10; // pause

key = 4’b0010; // set test signals value

#10; // pause

key = 4’b0011; // set test signals value

#10; // pause

key = 4’b0100; // set test signals value

#10; // pause

key = 4’b0101; // set test signals value

#10; // pause

key = 4’b0110; // set test signals value

#10; // pause

key = 4’b0111; // set test signals value

#10; // pause

key = 4’b1000; // set test signals value

#10; // pause

key = 4’b1001; // set test signals value

#10; // pause

key = 4’b1010; // set test signals value

#10; // pause

key = 4’b1011; // set test signals value

#10; // pause

key = 4’b1100; // set test signals value

#10; // pause

key = 4’b1101; // set test signals value

#10; // pause

key = 4’b1110; // set test signals value

#10; // pause

key = 4’b1111; // set test signals value

#10; // pause

end

// do at the beginning of the simulation

// print signal values on every change

initial

$monitor(«key=%b led=%b», key, led);

endmodule

Тестбенч починається з завдання масштабу часу і точності обчислення інтервалів:

`timescale 1ns / 1ps

Далі слід декларація модуля. Якби це було описом будь-якого пристрою, то далі було б опис портів модуля, але тестбенч не містить зовнішніх портів, а тільки внутрішні сигнали:

reg [4:1] key;

wire led;

Опис «провідника» «wire» вже раніше зустрічалося. Провідник не зберігає інформацію на відміну від «reg» — елемента зберігання даних, який зберігає значення сигналу до тих пір, поки йому не буде присвоєно нове значення.

Потім оголошується екземпляр модуля, який буде тестуватися. Тестована схема називається тестованим пристроєм (DUT, device under test) або testing модулем (UUT, unit under test). У нашому тестовому оточенні DUT описується наступним рядком:

lab1 dut (key, led);

Наступні рядки запускають initial блок:initial

begin

…

end

Кожен initial блок буде працювати тільки один раз, на початку моделювання. Якщо ж описано кілька початкових блоків, то вони будуть працювати паралельно.

В цьому розділі напишемо найпростіший тестбенч. Цей тестбенч буде подавати сигнали на входи модуля, що тестується через певні проміжки часу. У DUT є два входи, на які будуть подаватися послідовні сигнали з інтервалом в 10 одиниць модельного часу:

key = 4’b0000; // set test signals value

#10; // pause

Формат чисел, що подаються на входи, наступний: 4‘b0000. Це означає, що 4-бітний вектор з усіма бітами, рівними 0. 4‘b1111 відповідає 4-бітного вектору зі значенням 1111 в бінарному вигляді. Синтаксис «#» використовується для вказівки затримки. Це означає, що спочатку сигнал «key» буде встановлено в значення «0000». Потім (після затримки в 10 одиниць модельного часу) буде виконана наступна по порядку команда.

Наступний рядок містить команду:

initial $monitor(«key=%b led=%b», key, led);

Вона дає команду симулятора виводити всі зміни сигналів «led» і «key» на консоль.

Симуляція за допомогою ModelSim

Після виконання попередніх кроків ми маємо дві програми на мові VHDL – lab1.v та testbench.v. Також у нас встановлена програма ModelSim. Тепер за її допомогою виконанаємо симуляцію нашого проекту. Для цього виконаємо наступні дії:

Перейдемо до папки simulation, де запустимо скрипт симуляції у ModelSim (Листинг 1):

>01_simulate_with_modelsim.bat

У результаті виконання цього скрипта ви побачите результати моделювання вашоого коду.

Скрип з лістингу 1.3 запускає скрипт моделювання у пакеті ModelSim (Лістинг 1.4). Він написаний на мові TCL – скриптовій мові, що використовується пакетом ModelSim у якості внутрішньої мови для керування цим пакетом. Всі команди цього скрипта мають аналоги у графічному інтерфейсі пакету ModelSim, однак використання скриптів дозволяє значно скоротити роботу по симуляції та позбавитисть виконання однакових дій та зменшити час тестування.

Листинг 1.3 Скрипт ’02_simulate_with_modelsim.bat’

rem recreate a temp folder for all the simulation files

rd /s /q sim

md sim

cd sim

rem start the simulation

vsim -do ../modelsim_script.tcl

rem return to the parent folder

cd ..

Листинг 1.4 Скрипт ‘modelsim_script.tcl`

# create modelsim working library

vlib work

# compile all the Verilog sources

vlog ../testbench.v ../../lab1.v

# open the testbench module for simulation

vsim work.testbench

# add all testbench signals to time diagram

add wave sim:/testbench/*

# run the simulation

run -all

# expand the signals time diagram

wave zoom full

Більше на YouTube каналі: https://www.youtube.com/@ddlab-ua?sub_confirmation=1

Оставить комментарий